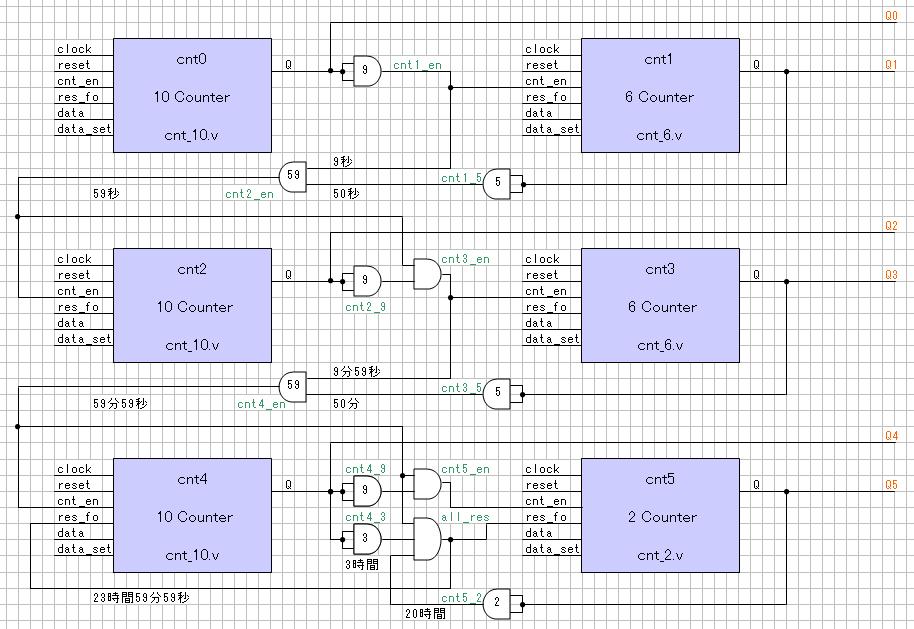

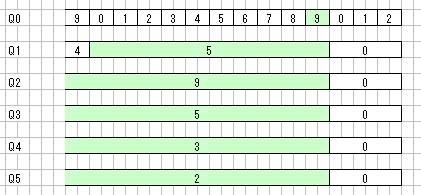

今までの回路だと、下位の桁だけをチェックしていたけど、1時間の位においては、20時間になった際&3:59:59になった際という条件でもリセットを行わなくてはいけない。

同様に、10時間の位もリセットの動作は23:59:59のタイミングで行わなくてはいけない。

方法としては、20時間になったという情報を1時間の位に送る。若しくは、1時間の位の内部に10時間の位に相当するカウンタを設けてそれを利用するなどが考えられる。また、リセットを行う条件の際にHになる信号を作り、その信号が入るとリセットされるように端子を設けるということも考えられる。

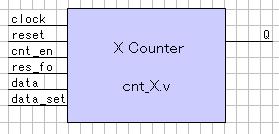

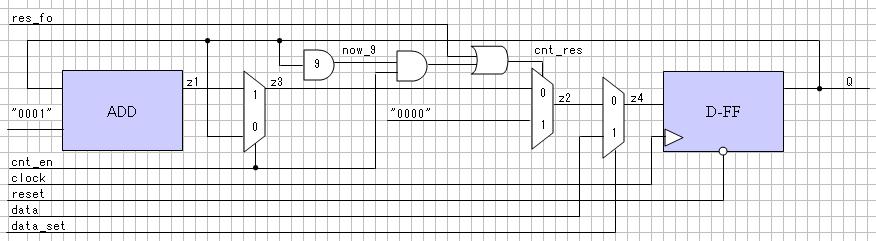

今回は、今後の使い勝手の事を考えて、リセット用の端子を新たに追加する。

module cnt_10(clock,reset,cnt_en,res_fo,data_set,data,Q);

input clock,reset,cnt_en,res_fo,data_set;

input [3:0] data;

output [3:0] Q;

reg [3:0] Q;

always @(posedge clock or negedge reset) begin

if (reset == 0)

Q <= 4'h0;

else if (data_set == 1'b1)

Q <= data;

else if (((Q == 4'h9) && (cnt_en == 1)) || (res_fo == 1))

Q <= 4'h0;

else if (cnt_en == 1)

Q <= Q + 4'h1;

else

Q <= Q;

end

endmodule

そして、青字の箇所をNに変更すれば、N進のカウンタが完成する。