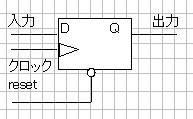

reset == 0で初期化を行い

入力Dを次のクロックでQに出力する。

always @(posedge clock or negedge reset) begin

if (reset == 0)

Q >= 0;

else

Q >= D;

end

key :

D-FF セレクタ 保持回路 パルス作成

002の続き

・D-FF

| 動作 | 記号 |

|

reset == 0で初期化を行い 入力Dを次のクロックでQに出力する。 |

|

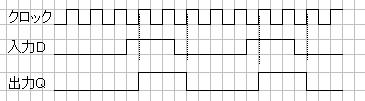

| VHDL記述 | タイミングチャート |

|

always @(posedge clock or negedge reset) begin if (reset == 0) Q >= 0; else Q >= D; end |

|

D-FF記述において、reset == 0の時の動作を書き忘れない事。

このように、外部から入力データを貰い受ける際にはそれほど大きな問題はないけれど、

出力Qを入力Dにフィードバックする際に初期値が定まらないとその後どんなにクロックが入力されようと

値が変化しないので・・・・

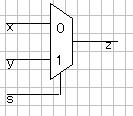

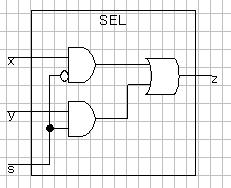

・セレクタ

| 動作・記述 | 記号 | ||||||||||||||||||||||||||||||||||||

|

セレクト信号sが0の場合、xをそのまま出力 1の場合、yをそのまま出力 z <= y when s = '0' else x; --z <= y when s = '0' else x + y; --error 条件分岐なので、そこで計算を行って出力するのは不可。 |

|

||||||||||||||||||||||||||||||||||||

| 真理値表 | 回路詳細 | ||||||||||||||||||||||||||||||||||||

|

|

z <= x when s else y;

z <= 真 when 条件 else 偽;

結構お世話になる記述。if文みたいな感覚で使えます。

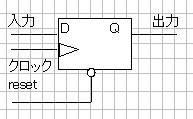

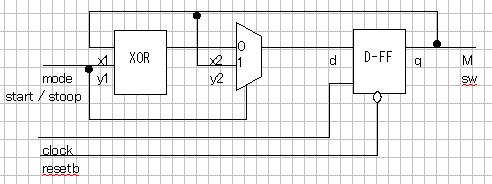

・保持

| 動作 | 記号 |

|

1shotのパルス信号を利用して、値を保持というか反転。 |

|

| VHDL記述 | タイミングチャート |

|

process (CLK,nRESET) begin if (nRESET = '0') then out_reg <= '0'; elsif(CLK'event and CLK = '1') then out_reg <= swich xor out_reg; else out_reg %lt out_reg; end if; end process; |

|

回路図で書くとちょっと複雑だけれど、記述は簡単♪

この記述において、最後のelseは実は無くても大丈夫。無かった場合は値を保持するようにできているから。

けれども、逆に考えると記述しなかったら勝手に保持されるため、思いもよらぬラッチ信号が出来てしまったりするので

elseを書いておく癖を付けるようにした方が良いかもしれない。

何度も言うようだけど、else if じゃなくて elsif

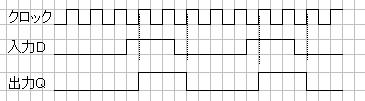

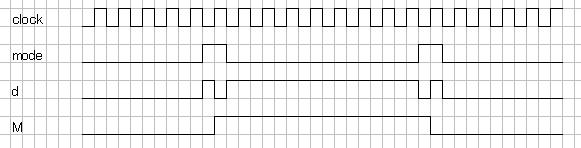

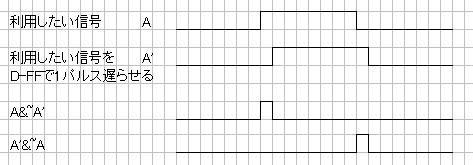

・パルス作成

| 動作 | 記号 |

|

非同期信号で回路を構成する際には必要ないかもしれないけど、 同期信号で回路を作らなくてはいけない場合が多いので安易に使いたい信号のnegedgeとかposedgeを使えないわけですよ。 そこで、使いたい信号を1度D-FFを通して1クロック分遅らせて元の信号と重ねれば・・・ |

|

| VHDL記述 | タイミングチャート |

|

process (CLK,nRESET) begin if (nRESET = '0') then okure <= '0'; elsif (CLK'event and CLK ='1') then okure <= inpal; end if; end process; outpal_reg <= not (inpal) and okure; |

|

この信号を利用して信号の立ち上がりや立下り時の動作を行う。

とりあえずこんなもん。